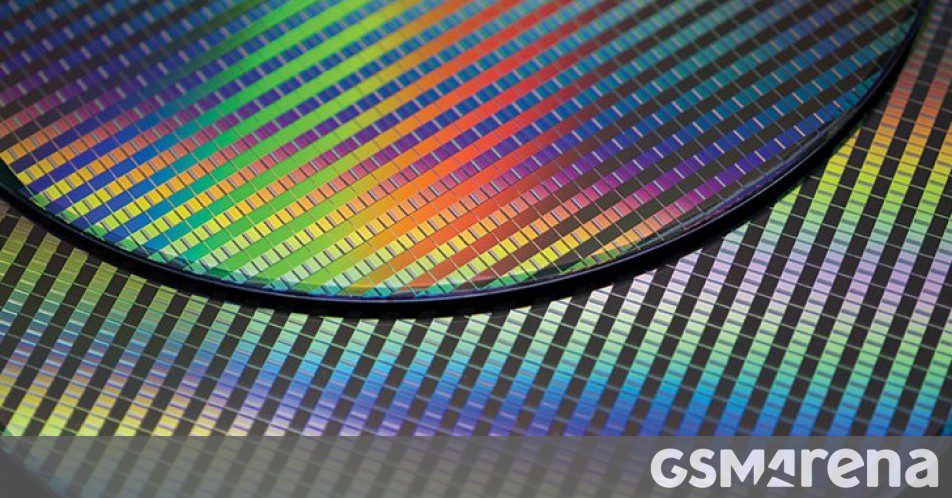

TSMC revealed its ground-breaking 1.6 nm production procedure for chips and it likewise consists of behind power shipment network that enhances power performance and transistor density even further.

The revealed 1.6 nm procedure depends on gate-all-around nanosheet transistors, much like the upcoming N2, N2P and N2X architectures based upon the 2nm node. The brand-new procedure alone enables 10% greater clock speeds at the very same voltage and approximately 20% lower power drain at the very same frequency and intricacy. Depending upon the chip style, the brand-new 1.6 nm procedure can likewise fit as much as 10% more transistors.

The behind power shipment network is perhaps a lot more excellent element of these future chips as it makes it possible for increased transistor density and enhanced power shipment, which in turn impacts efficiency. TSMC states that in addition to the Super Power Rail (SPR), which is the kind of plug utilized to conncect the chip to the source of power, the behind power shipment network will show advantageous primarily to AI and HPC processors that need complicated signal circuitry and thick power networks.

The production timeline is set up for the 2nd half of 2026, if all goes to strategy, with the very first consumer-ready items delivering in 2017.